- 本次主题由硅芯科技联合主办,InSemi半研咨询支持举办

前日,一场名为「异构集成新起点」的开放的闭门会,在这个元月、春马蹄声到来之前,AI芯片、光互连、堆叠芯片设计、先进封装四大话题多方参与,在“异构集成”这个技术交点上,悄然携手共话。本文为君带来此次活动要点回顾。

活动精选回顾

主办方:AI芯片和先进集成的新一轮联动

赵毅:AI大时代,异构集成下的EDA新范式

Jason Bai:端侧AI的新趋势、新变革、新发展

姚金鑫:异构集成在光计算系统中的作用与挑战

王书晓:赋能AI算力的硅光共封集成与STCO挑战

易敏:STCO方法论探讨,三维堆叠芯片高层次建模与验证方法

李云龙:混合键合技术赋能AI算力芯片

赵瑜斌:3Sheng Stratify物理验证EDA解决方案

关于活动&互动

活动系在张江之尚活动园区,由复旦大学校友总会集成电路行业分会发起的「AI大时代」系列沙龙,本次主题由硅芯科技联合主办,InSemi半研咨询支持举办。

复旦大学微电子学院副院长许薇在活动致辞中表示,人工智能的爆发式增长正在重塑半导体产业的技术架构。异构集成通过将不同工艺节点、不同功能模块、不同材料体系的芯片高效集成,开辟着"超越摩尔"的全新技术路径。她强调,复旦微电子学院在先进封装技术、三维集成电路设计、chiplet互连架构等方向持续深耕,愿与产业界携手推动异构集成技术从实验室走向产业化。

复旦大学校友总会集成电路行业分会秘书长、武岳峰资本合伙人刘剑也指出,AI大时代背景下,传统单芯片架构已难以满足算力爆炸式增长需求。Chiplet、3D堆叠、硅光集成等异构集成技术正在重新定义芯片设计和制造范式,这不仅是技术变革,更是产业生态的重构。他表示,复旦校友集成电路行业分会将持续搭建高质量交流平台,为校友企业赋能,助力异构集成技术和产业发展。

AI大时代:异构集成下的EDA新范式

“堆叠芯片技术是提升系统集成度与性能的关键路径,但其发展受限于工艺协同、设计方法、工具链及测试策略等多维度挑战。设计范式正从以芯片为核心的DTCO向以系统为核心的STCO演进。在此过程中,EDA工具的角色发生了根本性转变——从单一的设计工具升维为激活STCO技术和构建3DIC产业生态的桥梁。——在硅芯科技创始人兼总经理赵毅博士的主持和报告中开场。

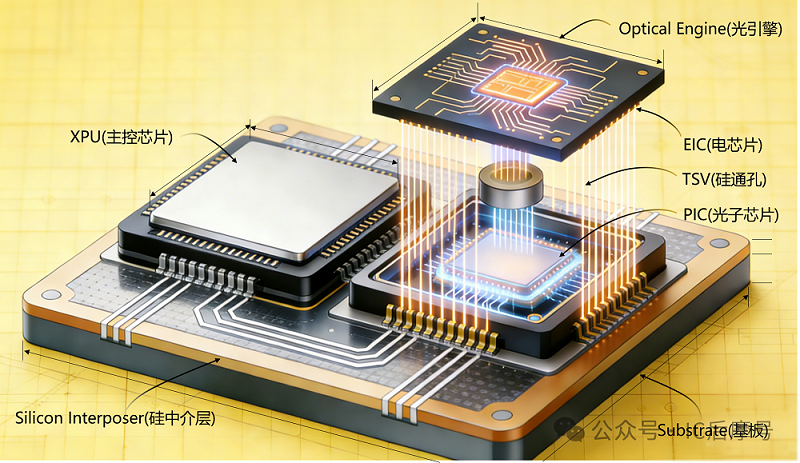

赵毅博士提出“EDA+新范式”,旨在通过构建覆盖“设计-制造-封装”的全流程数据闭环,将工艺约束与系统考量大幅“左移”至设计早期,从而减少迭代、降低成本。硅芯科技3Sheng EDA Platform是集“架构-物理设计-仿真分析-签核验证-容错”于一体的多芯片堆叠设计全流程开发平台,目前已有多个案例和重点项目在3Sheng EDA和设计方案落地。赵毅博士在STCO多个场景具有充分的实现闭环,本次特以光电共封装(CPO)为STCO的顶级场景,阐述了新范式下的EDA工具如何作为协同基石,实现复杂的系统异构集成。

端侧AI:多维挑战催生技术革新

光羽芯辰联合创始人兼副总裁Jason Bai代表AI算力应用侧需求,首先强调的是端侧AI正当时。端侧AI对功耗、尺寸的极致要求与多样化应用需求,正倒逼设计方法与3D异构集成技术革新。光羽芯辰自主研发的EdgeAIon(存算一体架构+3D异构集成技术)端侧AI解决方案芯片实现了更高能效、带宽及更低延迟,完全满足了大模型在智能终端的顺畅运行。

然而短期内,端侧AI在软件生态上缺乏统一的开发平台和工具链,导致应用开发成本高、周期长,在硬件方面又面临算力和功耗依然制约终端设备在端侧AI的发展,以及端侧AI在普及过程中不断带来新的数据安全和隐私保护等诸多挑战。

随着AI Agentic APP在当下的大面积应用all-for-all普惠,在消费电子、汽车、工业等各行业的智能升级,势必面对算力更丰富、垂直应用更智能、安全和便捷的终端设备需求增长,端侧AI正迎来前所未有的发展浪潮。

而面对这样的浪潮Jason Bai总提出,一个开放、健康的生态是端侧AI产业发展的关键。目前在软硬件开发的生态上,需要持续往前走,通过开源模型、开源框架和行业标准的建立,可以降低开发门槛,促进技术创新,加速产业落地。持续推动技术创新与生态融合,以实现更广泛的落地应用。

异构集成在光计算系统中的作用与挑战

光本位科技是光电计算、AI智算集成硬件交叉领域的明星企业,光本位科技产品与市场副总裁姚金鑫(J叔),直接从AI计算与光子学发展的角度来看异构集成在光计算系统中的作用与挑战。姚总从晶圆级-芯片级-系统级和组件异质的四个层面探讨了目前异构集成的需求和挑战。

从CPO和3D堆叠的典型架构上,驱动器和TIA垂直堆叠在光调制器和探测器上,在互连中需要TSV和微凸块实现微米级垂直互连,要求寄生效应最小化,性能需要达到单向带宽100Tbps级,带宽密度450Gbps/mm。虽然光模块因为产业相对成熟面积可做得较大,足以支撑各种散热架构,但是当光模块做成一块芯片级的设计,从体积、散热,在IO die和数字逻辑芯片的热耦合问题就比较大了。

从亚微米级的系统级异构的光耦合挑战来看,光模块与基于switch的芯片不同,XPU在异构封装中由于尺寸较小,OE无法放置ODSP,涉及多种芯片和耦合问题。光口避让和翘曲等问题带来的结构设计复杂性,以及系统链路信号对于光电接口、光学链路的误差、抖动部分的低容忍度都在设计中会遇到;且在亚微米级的对准精度要求,微小的偏差会带来光学链路插损增大,影响链路稳定性和误码率,以及温度对光学封装耦合接口部分的可靠性问题。

组件的异质集成,需要在聚合物主办上集成激光器阵列、光纤阵列与驱动芯片。更多的情况是在集成数字逻辑、光芯片、数模混合等芯片,如何确保耦合效度?多组件在集成时,直接的问题是其工艺、材料、平台、标准可能均不一样,所以统合的问题就会比较多。这就希望有类似是会的交流,借助EDA、Fab、OSAT和设计公司遇到的问题能按照某种节奏,一点一点去统合起来解决;以及从业态或生态构建,涵盖通讯、计算、存储、制造个环节的工具与软件,不能独立、单领域解决。

赋能AI算力的硅光共封集成与STCO挑战

上海微系统所副研究员王书晓博士在本次话题交流中,清晰阐述在AI数据中心架构驱动下的CPO和OIO应用场景、技术、产品布局和当下的可行技术方案,特别对于STCO的主要研究和实践做了具有全局观和更为详尽的梳理。

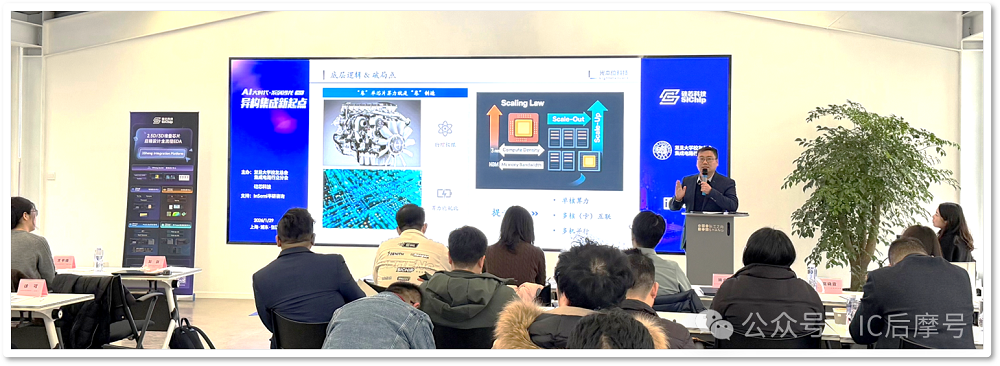

和传统IC设计与DTCO不同的是,STCO是系统优先,全局协同。从设计流程上来讲,根据工作负载,传统SoC分解为多个Chiplet,为计算、存储、I/O等模块匹配最优工艺,这是在顶层进行功能分解与架构重塑;在2.5D/3D封装的硅中介层、混合键合技术中,不同工艺、功能芯粒/模块的高密度高性能集成,是在物理实现阶段的多目标设计协同;对最终系统的电、热、应力、供电网 络等进行全局仿真与优化,确保性能释放与可靠性是多物理效应对系统保障的最终协同设计与优化。从系统分解-封装集成-多物理协同三级联动,是STCO将系统需求精准转化为可实现物理方案的必由途径。

从技术和方法上,STCO一方面是Chiplet互连标准和先进封装工艺,在硬件实现上基础使能方法的存在,包括各家标准对不同工艺芯粒即插即用的定义,混合键合等技术、封装材料探索在互连性能突破上限;另一方面是在EDA工具在系统-封装-芯片跨层级协同设计、面对电热力磁多物理仿真分析,以及AI驱动设计空间探索上工具自动化的从点到面。

在基于硅光技术的STCO领域,王书晓博士提到多个新挑战。

来自>500W/cm²封装热密度、协同变量指数级增长,以及光学性能和物理环境强关联带来的设计挑战。

封装顺序和集成路径抉择会影响设计复杂度与最终良率,这对集成精度和工艺兼容性的要求自然飙升。对准精度、热管理、工艺兼容性、电互连难度均是封装顺序要直面选择变量,而设计规则、工艺阶段、热预算在晶圆级的对齐和协同,会让STCO面临终极考验。

失效模式从电学故障转向光电交叉故障,由于光耦合老化、热循环偏移导致光损的存在,导致失效模式存在光电交叉故障,传统电测方法束手无策, STCO需在设计中融入光学可测性设计,建立跨域故障模型。

以及面对光电技术跨领域的情况,材料、设计工具链、统一PDK、标准等各方面的供应链严重碎片化,STCO之路仍需跨领域定制协同策略,跨企业、跨平台的协同成本与风险均剧增。

STCO方法论探讨:三维堆叠芯片高层次建模与验证方法

上创EDA/IP中心技术总监易敏老师,是新一代DVM(分布式验证模型)验证平台在EDA和IP领域的资深践行者,由于高层次建模、高层次综合、高层次验证在多芯片/多模块、堆叠架构、先进封装芯片领域的发展还在早期,整个产业链在大规模分布式并行验证,以及逻辑和物理联合仿真都比较薄弱。故本次借异构集成设计角度,易敏老师首先提出的是逻辑系统和物理系统验证双向驱动、闭环迭代的重要性,随后就其验证平台方法探讨解决方案。

一方面,逻辑建模和验证对于物理电路模型、物理验证是正向驱动的。逻辑设计定义的架构、接口与性能目标,直接决定物理封装的互连方案、堆叠方式与选型。另一方面,物理设计对于逻辑综合又是反向约束的。物理实现的现实约束(如互连寄生、热极限、成本)将反馈至逻辑设计,驱动架构、接口的调整,以确保可制造性与可靠性。

两者在统一数据平台的基础上,在设计过程持续协同。逻辑阶段预估物理特性进行前向的权衡,在物理实现中的寄生、热数据反标回逻辑验证,最终系统签核需同时满足逻辑正确与物理可靠,形成完整设计闭环。

首先,在设计左移方法升级上,需要从多维物理效应与逻辑行为双方面进行紧耦合验证。需要构建能高效定义多维度参数组合、实现跨域数据无缝互通的验证环境,以系统覆盖各类工作场景与边界条件,支持跨域数据协同仿真。

其次,多芯粒/多模块验证不可避免的是架构迭代的评估方法,对多参数耦合的情况需要进行完备的量化评估,以及系统级寻优。其关键挑战在于将“场景完备性”量化维覆盖率等指标,并构建高效的“仿真-反标”闭环,在性能、功耗、面积等多目标约束下实现数据驱动的权衡与最优决策。

再次,工具链执行效率始终是大规模验证的痛点,多核/分布式仿真加速技术需要持续应用落地。如果能构建统一的协同验证平台,比如以标准化接口支持芯粒快速集成与重组,同时实现高效多核/分布式仿真,即可应对系统规模增长与频繁迭代带来的验证复杂度。

最后,对于从统一平台架构与模型复用、多仿真器协同、参数与数据互通、系统级分析与收敛以及迭代效率提升上,易敏老师总结到目前需要EDA+新范式创链的概念。

混合键合技术对AI芯片系统的赋能

本次活动还有幸请到浙江大学集成电路学院求是特聘教授李云龙老师,李教授从先进封装工艺角度阐述了发展中的AI芯片3DIC工艺的发展的当前关键技术。一是在SiCN粗糙度直接影响键合强度,目标是RMS 0.10nm,表面清洁、后CMP控制以及减少颗粒污染至关重要。其次,Cu焊盘的凹陷深度与形状会直接影响键合强度及其电导率,及芯片系统整体的性能和能效比;以及铜-铜接触控制在避免空洞的技术,在金属高度、CET匹配的退火温度,以及Cu薄膜质量、纯度、等级、晶粒尺寸等方面的严格控制。

李老师总结到,AI芯片可靠性与数据传输速率和提升导致能耗显著增加,互连微缩路径的混合键合技术,通过微缩互连间距、实现铜-铜直接键合与介质层集成,在提升I/O密度的同时,根本性降低功耗、改善信号完整性。

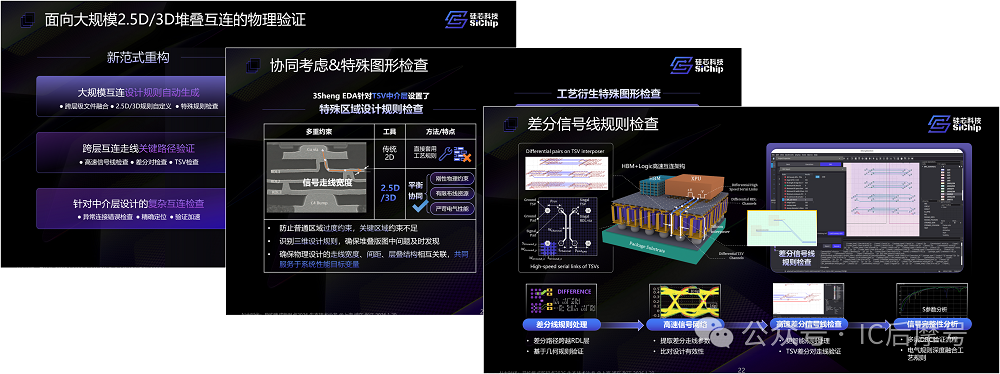

3Sheng Stratify 物理验证EDA工具和解决方案

对于硅芯科技赵毅博士提到的本次活动如何将这一新范式转化为可落地、可验证的工程能力?硅芯科技在本次会上带来了最新的产品解决方案发布。产品市场经理赵瑜斌(Robin)针对堆叠架构的复杂互连集成工具——提供“3Sheng Stratify物理验证设计解决方案”。

本次硅芯EDA在物理验证工具和方案的发布,也是在堆叠芯片设计范式上创新实践之一。从传统IC内DRC/LVS升维到了跨IC-中介层-基板级的规则和一致性验证:工具支持大规模互连的设计规则自动生成、跨层互连走线关键路径的左移验证、针对中介层设计的复杂互连检查验证,以及机器学习聚类强化的连接走线的自动检查。从二维的DRC升维到了跨芯粒和封装间,从传统的版图原理图一致性验证增维到了物理连接完整性的检查。并且预告在后续会持续推出在架构设计-物理仿真协同-物理验证连续工具和方案的迭代路径。

该系列沙龙以2026「AI大时代」为背景,在即将到来的端侧AI广泛应用、驱动算力提升的软硬件技术、支撑算力芯片各领域多架构提出和实现等核心话题上实现学术和产业闭环的交流探讨与合作创造,欢迎更多的专家和机构加入、参与和合作。

评论

赞

赞

收藏

收藏

评论

评论

搜索

搜索

写点什么吧~